# Fifty Applications of the CMOS Inverter—Part 1

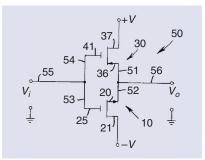

The CMOS inverter dates back to a patent filed by Wanlass in 1963 [1]. Shown in Figure 1 is the disclosed structure. (Unlike today's convention, Wanlass denotes the drains by arrows.) With the scaling of the supply voltage in nanometer technologies, the CMOS inverter has found much wider application, and many of its properties have come into focus. In this multipart article, we study 50 examples of circuits using inverters in critical roles. Moreover, we use simulations to quantify the performance of these topologies. Simulations are performed in the slow-slow corner of 28-nm technology at  $T = 75^{\circ}$  C, with  $V_{DD} = 0.95$  V. An estimate of the layout parasitic capacitances is also included. Unless otherwise stated, L = 30 nm for all transistors.

It is important to recognize the poor supply rejection of inverters. That is, the small-signal voltage gain from their supply to their output is comparable to that from their input to their output. For this reason, many of the circuits studied in this article require operation from lownoise voltage regulators.

#### **The Tapered Buffer**

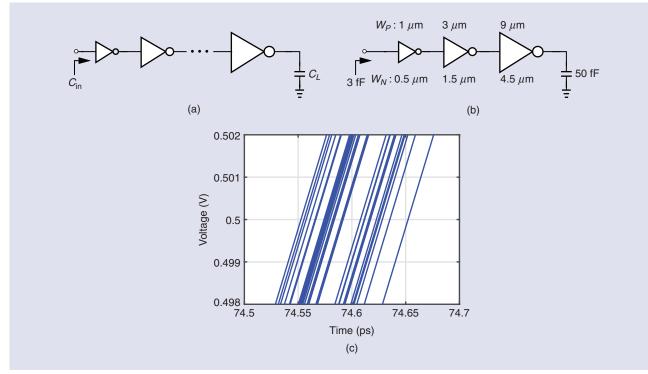

Among the oldest applications of the inverter, the tapered buffer consists of a cascade of scaled stages optimized for minimal delay for driving a given capacitance,  $C_L$  [Figure 2(a)]. It can be shown that a scaling factor

Digital Object Identifier 10.1109/MSSC.2024.3419528 Date of current version: 23 August 2024 of  $e \approx 2.718$  minimizes the delay if the drain capacitances of the transistors are neglected. Under this condition, the stages contribute equal delays. The number of stages is given by  $n = \ln(C_L/C_{in})$ , where  $C_{in}$ denotes the input capacitance of the first stage. If drain capacitances are included, the scaling factor is greater, e.g., around three to four.

In addition to the delay, the power consumption of the cascade is also of interest. The total capacitance for the tapered stages is equal to

$$C_{\text{tot}} = C_{\text{in}} + eC_{\text{in}} + e^2C_{\text{in}} + \dots + e^nC_{\text{in}}$$

<sup>(1)</sup>

$$e^{n+1} - 1$$

(2)

$$= \frac{1}{e-1} C_{\text{in}}$$

(2)

$$=\frac{eC_L-C_{\rm in}}{e-1}.$$

(3)

The total power is thus given by

$$P = f_{\rm in} \frac{eC_L - C_{\rm in}}{e - 1} V_{\rm DD}^2 \tag{4}$$

where  $f_{in}$  is the input frequency.

In wireless and wireline transceivers, the tapered buffer is used to drive long interconnects carrying

**FIGURE 1:** The CMOS inverter patented by Wanlass.

local oscillator (LO) waveforms or clocks. In such environments, the delay may be less problematic, but the jitter introduced by the chain proves critical. To minimize jitter, we wish to sharpen the voltage transitions at the output of each stage.

As an example, we design a buffer for driving  $C_L = 50$  fF at  $f_{in} = 10$  GHz. Depicted in Figure 2(b), the circuit employs an input inverter with  $W_N = 0.5 \ \mu\text{m}$  and  $W_P = 1 \ \mu\text{m}$ , exhibiting an input capacitance of about 3 fF. We thus have  $n = \ln(C_L/C_{in}) \approx 3$ . Scaling the next two stages by factors of three and nine, respectively, yields a delay of 22 ps. Simulations indicate  $P_{\text{tot}} = 740 \ \mu\text{W}$ , slightly greater than the 700  $\mu\text{W}$  predicted by (4) and arising from the inverters' crowbar current.

We compute the buffer's jitter by running a transient noise simulation for 100 ns, wherein a noise frequency range of 10 MHz to 300 GHz is specified. Provided in Figure 2(b), the eye diagram transitions reveal a peak-topeak jitter of 100 fs, which translates to an RMS value of about 17 fs if we assume the peak-to-peak value of the Gaussian noise is roughly six times its standard deviation.

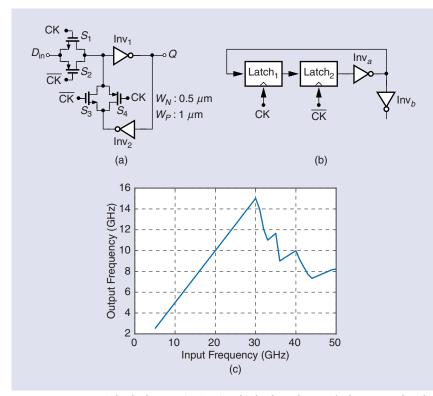

#### The T-Gate Static Latch

For digital or mixed-signal designs that must accommodate arbitrarily low clock or refresh rates, we incorporate static latches. For example, a system that performs foreground calibration must retain the settings indefinitely after power-up. The latch presented in Figure 3(a) is such

FIGURE 2: (a) The tapered buffer, (b) an example, and (c) its output jitter.

a candidate. In the sense mode,  $D_{in}$  travels through  $S_1$ ,  $S_2$ , and  $Inv_1$ , and in the store mode, it is held by  $Inv_1$ ,  $Inv_2$ ,  $S_3$ , and  $S_4$ .

A quick method of evaluating the speed limitations of latches is to incorporate them in frequency dividers, specifically in  $\div 2$  circuits.

FIGURE 3: (a) A static latch, (b) a ÷2 circuit using this latch, and (c) an I/O frequency plot of the divider.

Shown in Figure 3(b) is such a structure, where  $Inv_a$  provides a net inversion around the loop and  $Inv_b$  acts as a buffer. With rail-to-rail voltage swings for *CK* and *CK*, we plot the output frequency versus the input frequency in Figure 3(c), observing failure beyond  $f_{in} = 30$  GHz. Since the loop can sustain a periodic waveform at 15 GHz, we expect the static latch to handle data rates up to about 15 Gb/s. The divider draws 300  $\mu$ W at 30 GHz.

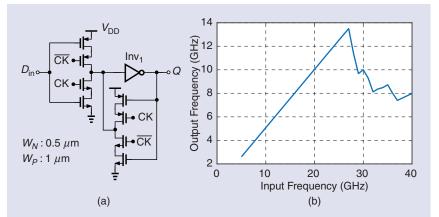

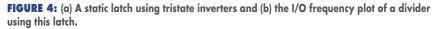

## **The Tristate Static Latch**

Another static latch topology employs tristate inverters rather than T gates [2]. Depicted in Figure 4(a), the circuit reduces to two cascaded inverters in the sense mode and two cross-coupled inverters in the store mode. The reader may recognize the input and feedback stages as "clocked CMOS" (C<sup>2</sup>MOS) logic, but they do not act as latches here. As in Figure 3(b), we construct a  $\div 2$  circuit using this type of latch and evaluate its performance. Plotted in Figure 4(b), the I/O frequency behavior suggests a maximum speed of 27 GHz. Thus, this topology is slower than that in Figure 3(a). The  $\div$  2 stage draws 300  $\mu$ A at this frequency.

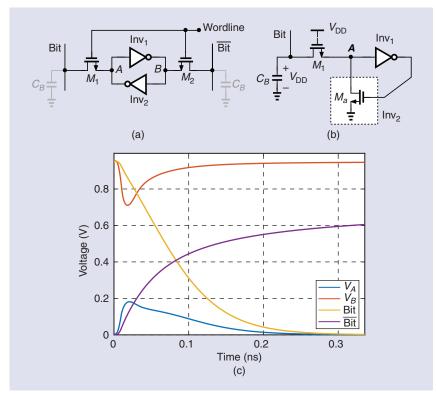

### The Set–Reset Latch

Set–reset (SR) latches can be used to hold data asynchronously. Depicted in Figure 5(a), the structure consists of two cross-coupled inverters controlled by input devices  $M_1$  and  $M_2$ . If, for example,  $\bar{Q} = 1$  and only *S* goes high, then  $\bar{Q}$  falls, and *Q* reaches a logical one. Since  $M_1$  and  $M_2$  must overcome the PMOS transistors within Inv<sub>1</sub> and Inv<sub>2</sub>, the circuit exemplifies "ratioed" logic. The inverters' NMOS transistors play a minor role in the SR operation, but they prove necessary for retaining the state if the latch must hold the data for a long time.

To assess the speed of the circuit, we place two instances of it in a loop so as to form a quadrature ring oscillator, as in Figure 5(b). We have  $W_P = 2W_N = 1 \,\mu m$  for the inverters, and  $W_{1,2} = 1 \,\mu m$ . Plotted in Figure 5(c), the output waveforms reveal a frequency of 18 GHz and, hence, a delay of about  $1/(4 \times 18 \,\text{GHz}) = 14$  ps per latch.

#### The Dynamic Latch

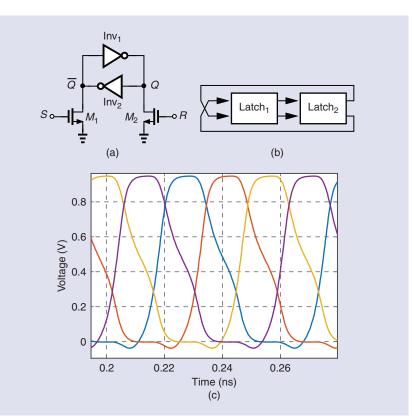

A simple dynamic latch can be realized by means of a T-gate and an inverter [Figure 6(a)]. In the sense mode, the circuit allows  $V_X$  to track  $D_{in}$ , and in the store mode, it holds the data on the total capacitance at this node. Note that the charge injection and clock feedthrough of T-gate devices may degrade the high and low values at *X*. The inverter restores the logical levels and prevents charge sharing with the next stage.

We construct the arrangement of Figure 3(b) for this latch as well. With  $W_2 = 2W_1 = 1 \mu m$  and the same widths for the inverter devices, we arrive at the I/O frequency plot in Figure 6(b). The circuit operates up to 44 GHz and consumes 250  $\mu$ A at this frequency, proving superior to the static counterparts studied above.

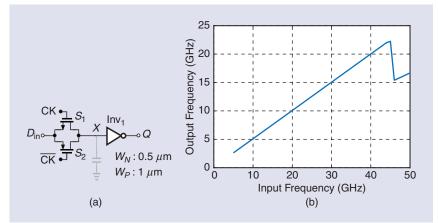

## The Static Memory Cell

The cross-coupled inverters encountered in the SR latch can also hold a state in a static memory environment. For this purpose, the cell must be able to sense a state (in a "write" operation) and deliver a state (in a "read" operation). Illustrated in Figure 7(a), the circuit employs "access" devices  $M_1$  and  $M_2$  for both operations. Differential outputs improve the read speed.

Owing to the large bit line capacitance,  $C_B$ , a read operation may destroy the cell's state. Consider the situation in Figure 7(b), where Bit = 1 but the cell holds a zero at *A*. When  $M_1$  turns on, it acts as a source follower, raising  $V_A$ . If  $V_A$  reaches the switching threshold of Inv<sub>1</sub>, this inverter, and, hence, the entire cell, may change its state. Thus,  $M_a$  must be strong enough to avoid this effect.

Plotted in Figure 7(c), the cell's waveforms after the word line rises reveal that  $V_A$  reaches 0.2 V, still retaining the state. With  $C_B = 40$  fF, Bit

FIGURE 5: (a) An SR latch, (b) a ring oscillator using such a latch, and (c) oscillator output waveforms.

FIGURE 6: (a) A dynamic latch and (b) the I/O frequency plot of a divider using this latch.

FIGURE 7: (a) A static memory cell, (b) the circuit in the read mode, and (c) the circuit's waveforms.

and Bit evolve rather slowly, an issue alleviated through the use of a differential sense amplifier (not shown).

#### **The Low-Noise Amplifier**

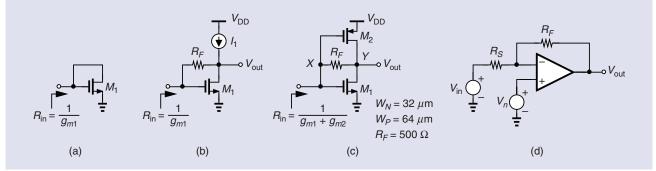

The LNAs used in RF receivers must present an input resistance of  $50 \Omega$ , a low noise figure (NF), and a reasonable gain. The CMOS inverter is one such candidate.

Beginning with the diode-connected transistor in Figure 8(a) and neglecting channel length modulation, we recognize that the device exhibits a small-signal resistance equal to  $1/g_{m1}$ . The topology in Figure 8(b) provides the same  $R_{in}$  because  $R_F$  appears in series with an ideal current source in the small-signal model. However, current source  $I_1$  contributes noise without carrying the input signal. We thus convert  $I_1$  to an "active" load, as illustrated in Figure 8(c), expecting an input resistance of

$$R_{\rm in} = \frac{1}{g_{m1} + g_{m2}} \tag{5}$$

which can be set to  $50 \Omega$ . It can be proved that proper input matching places a lower bound of 3 dB on the NF.

Equation (5) appears to imply that  $R_F$  does not experience the Miller effect. However, computing the voltage gain from *X* to *Y*, we have  $A_v = 1 - (g_{m1} + g_{m2})R_F$ , and hence,  $R_{\text{in}} = R_F/(1 - A_v) = 1/(g_{m1} + g_{m2})$ .

In practice, the finite output resistance of  $M_1$  and  $M_2$  alters our results considerably. One can show that  $R_{in}$ in Figure 8(c) is now expressed as

$$R_{\rm in} = \frac{R_F + r_{O1} \| r_{O2}}{1 + (g_{m1} + g_{m2})(r_{O1} \| r_{O2})}.$$

(6)

FIGURE 8: The (a) impedance of a diode-connected device, (b) input impedance of the device with a feedback resistor, (c) basic LNA, and (d) simple model for noise calculation.

FIGURE 9: The LNA's (a) NF, (b) gain, and (c) return loss.

As an example, with  $W_1 = 32 \,\mu\text{m}$ ,  $W_2 = 64 \,\mu\text{m}$ , and a bias current of 5.5 mA, we have  $g_{m1} + g_{m2} \approx 44 \,\text{mS}$  and  $r_{O1} \parallel r_{O2} = 90 \,\Omega$ . It follows that  $R_{\text{in}} = (R_F + 90 \,\Omega)/9 = R_F/9 + 9 \,\Omega$ . We observe that for  $R_{\text{in}} = 50 \,\Omega$ ,  $R_F$  must not exceed 370  $\Omega$ . Interestingly, the low output resistance of the transistors makes  $R_F$  a greater contributor to  $R_{\text{in}}$  than  $1/(g_{m1} + g_{m2})$ .

The dependence of  $R_{in}$  upon  $R_F$ also rewrites the NF equation. Drawing the circuit as in Figure 8(d), where  $V_n$  denotes the inverter's inputreferred noise, we have

$$V_{\text{out}} = -\frac{R_F}{R_S} V_{\text{in}} + \left(1 + \frac{R_F}{R_S}\right) V_n.$$

(7)

It follows that

$$NF = 1 + \frac{\left(1 + \frac{R_F}{R_S}\right)^2 \overline{V_n^2}}{4kTR_s \left(\frac{R_F^2}{R_S^2}\right)}.$$

(8)

We now assume  $R_F \gg r_{O1} || r_{O2}$  and  $(g_{m1} + g_{m2})(r_{O1} || r_{O2}) \gg 1$  in (6) and

write  $R_{in} \approx R_F / [(g_{m1} + g_{m2})(r_{O1} || r_{O2})] = R_S$ . We also assume  $R_F \gg R_S$  in (8), arriving at

$$NF \approx \gamma \frac{r_{O1} \parallel r_{O2}}{R_F} + 1.$$

(9)

The NF no longer faces a lower bound of 3 dB. In our numerical example,  $(r_{O1} || r_{O2})/R_F \approx 0.24$ , and NF  $\approx 1.9$  dB. These calculations have neglected the noise of  $R_F$ .

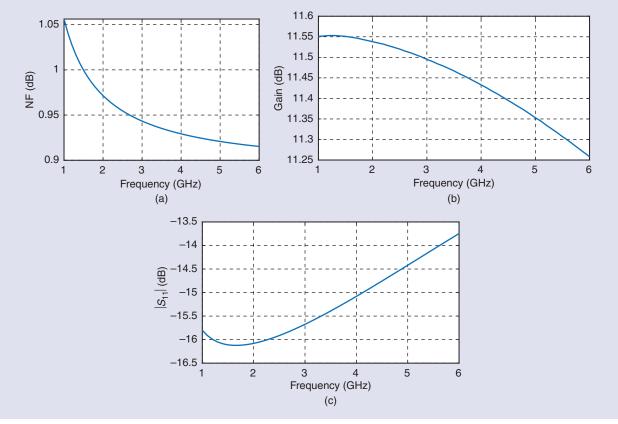

We simulate the LNA with the numerical values mentioned

above but with  $R_F = 500 \Omega$  so as to reduce both its noise contribution and the first term in (9), even though it leads to  $R_{in} \approx 66 \Omega$ . Figure 9(a) plots the NF for a frequency range of 1–6 GHz, displaying a peak value of 1.05 dB (due to flicker noise). The power consumption is 5.2 mW. We note from Figure 9(b) that the gain from  $V_{in}$  to  $V_{out}$  in Figure 8(d) is about 11 dB. Figure 9(c) reveals an acceptable range for the input return loss,  $|S_{11}|$ .

FIGURE 10: (a) A self-biased inverter following an oscillator and (b) the circuit's gain.

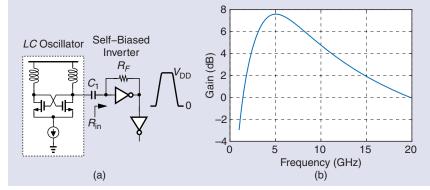

#### **The Self-Biased Inverter**

The topology of Figure 8(c) can be modified so as to serve other

purposes as well. Displayed in Figure 10(a), the "self-biased inverter" acts as an amplifier and proves

FIGURE 11: (a) The effect of a dc offset on the inverter output duty cycle, (b) the duty cycle correction circuit, and (c) the input and output waveforms.

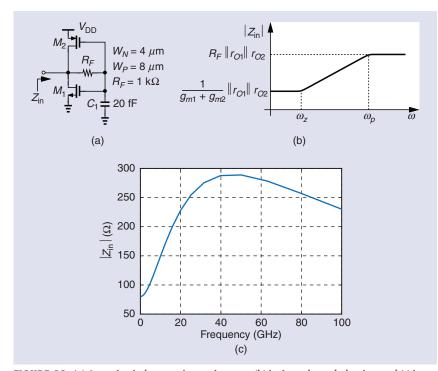

FIGURE 12: (a) An active inductor using an inverter, (b) its impedance behavior, and (c) its simulated impedance.

particularly useful if rail-to-rail voltage swings are sought. For example, an *LC* oscillator delivering moderate swings with a common-mode level near  $V_{DD}$  can be followed by this stage, thus providing a rail-to-rail output.

The value of  $C_1$  in Figure 10(a) is governed by two considerations. First, it must be about 10 times the input capacitance of the inverter to minimize attenuation. Second, it must be sufficiently large so that the high-pass corner frequency,  $1/(2\pi C_1 R_{in})$ , falls well below the lowest frequency traveling through the circuit.

We scale the LNA of Figure 8(c) down by a factor of 32, arriving at  $W_N = 1 \ \mu m$ ,  $W_P = 2 \ \mu m$ ,  $I_D = 170 \ \mu A$ , and  $r_{O1} \| r_{O2} = 2.9 \ k\Omega$ . Figure 10(b) plots the small-signal gain of such a design with  $C_1 = 30 \ \text{F}$ , revealing a high-pass corner around 2.5 GHz and a peak gain of 7.5 dB at 6 GHz. Beyond 20 GHz, the circuit begins to lose its efficacy for a fanout of one.

The input resistance merits a great deal of deliberation. Equation (6) yields  $R_{in} = (R_F + 2.9 \text{ k}\Omega)/9$ ; e.g.,  $R_{in} = 1 \text{ k}\Omega$  if  $R_F = 6.1 \text{ k}\Omega$ . Unfortunately, an input resistance of  $1 \text{ k}\Omega$  can significantly lower the tank *Q* in Figure 10(a). Fortunately,  $R_{in}$  is much higher if the VCO output swing is large enough to cause large-signal operation in the inverter. Nonetheless, the phase noise of the VCO must be closely examined before and after the self-biased inverter is attached.

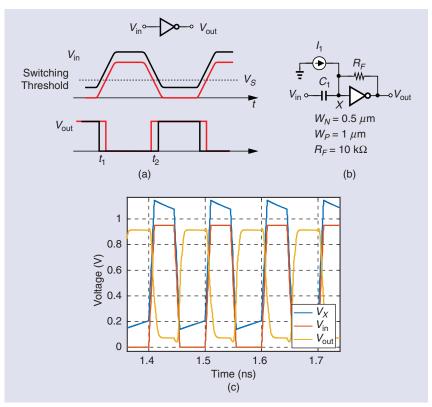

#### The Duty Cycle Correction Circuit

High-speed systems face tight timing constraints, often demanding a precise 50% duty cycle for their clocks. Moreover, if a clock or LO waveform is applied to a  $\div$  2 circuit to generate quadrature phases, the output phase accuracy dictates a 50% duty cycle for the input. To arrive at a duty cycle correction circuit, we begin with the input waveforms in Figure 11(a), assuming, for simplicity, that  $V_{out}$  jumps as  $V_{in}$  crosses the switching threshold of the inverter,  $V_{S}$ . We observe that a vertical shift in  $V_{in}$  alters the times at which

$V_{in}$  crosses  $V_{S}$ , a property afforded by the finite rise and fall times of  $V_{in}$ . As a result, the inverter output duty cycle changes. Specifically, for an input offset of  $+\Delta V, t_2 - t_1$  increases by  $2\Delta V/S$ , where *S* denotes the input slew rate.

The self-biased inverter provides a simple environment for this cor-

rection method. As demonstrated in Figure 11(b) [3], we inject current  $I_1$  into the input node, creating a departure equal to  $I_1 R_{in}$  from the inverter's switching threshold, where  $R_{in}$  is given by (6). The output low level thus lasts longer by  $2I_1 R_{in}/S$ .

The topology of Figure 11(b) faces two issues. First, it offers a narrow

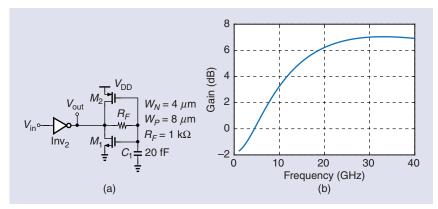

FIGURE 13: (a) A CTLE using an active inductor and (b) its frequency response.

correction range if  $V_{in}$  exhibits fast transitions. As seen in the simulation results presented in Figure 11(c) for an input frequency of 10 GHz and rise and fall times of 10 ps, we can improve a duty cycle of 45% to 48% with  $I_1 = 10 \ \mu$ A and  $R_F = 10 \ k\Omega$ . This is expected, as  $S = 0.95 \ V/10 \ ps$ ,  $I_1 R_{in} = 180 \ mV$ , and, hence, the correction amounts to only 3.8 ps. One can cascade multiple stages to widen this range.

Second, Figure 11(a) and (c) reveals that the inverter input, in fact, rises above  $V_{DD}$  (or falls below ground), possibly stressing one of the inverter's transistors.

#### **The Active Inductor**

It is possible to configure a feedback loop such that it presents an inductive input impedance across some frequency range, hence the term "active inductor."

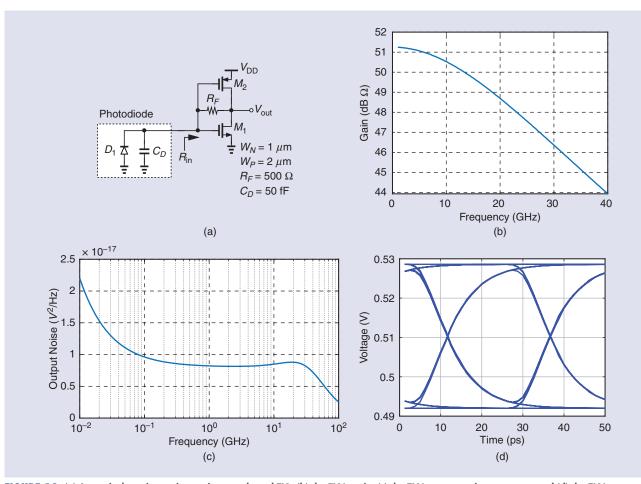

FIGURE 14: (a) An optical receiver using an inverter-based TIA, (b) the TIA's gain, (c) the TIA's output noise spectrum, and (d) the TIA's output eye diagram.

The self-biased inverter studied in previous sections can create such an impedance. As illustrated in Figure 12(a) [4], at low frequencies,  $Z_{in} = (r_{O1} || r_{O2}) || (g_{m1} + g_{m2})^{-1}$ , a low value, and at high frequencies,  $Z_{in} = (r_{O1} || r_{O2}) || R_F$ , a large value [Figure 12(b)]. The equivalent inductance is roughly equal to  $R_F C_1/$  $(g_{m1} + g_{m2})$ . Figure 12(c) plots this behavior for  $R_F = 1 \text{ k}\Omega$ ,  $C_1 = 20 \text{ fF}$ ,  $W_N = 4 \ \mu m$ , and  $W_P = 8 \ \mu m$ . The slope of  $|Z_{in}|$  beyond the zero frequency yields L = 1.4 nH, somewhat close to the theoretical value of  $R_F C_1 / (g_{m1} + g_{m2}) = 1.9 \,\mathrm{nH}.$

The response depicted in Figure 12(c) is reminiscent of that of continuous-time linear equalizers (CTLEs). We can then utilize the circuit as the load of another inverter so as to construct a CTLE [4]. Illustrated in Figure 13(a), such an arrangement proves attractive, as it consumes less voltage headroom than topologies using differential pairs. Figure 13(b) displays the resulting small-signal behavior, revealing 9 dB of boost around 20 GHz. The circuit consumes 0.65 mW. Of course, the common-mode level of the data arriving at the input of Inv<sub>2</sub> must be accurately set so as to ensure that this inverter does not fight the bias point of  $M_1$  and  $M_2$ .

### The Transimpedance Amplifier

In optical communication receivers, a photodiode converts the light intensity provided by a fiber to an electric current. A TIA is thus necessary to transform this current to a voltage. The input resistance, bandwidth, and noise of the TIA prove critical here.

As evident in Figure 14(a), an optical receiver front end must present a low resistance,  $R_{in}$ , to the photodiode's capacitance to guarantee sufficient bandwidth for the incoming data. In a manner similar to the LNA of Figure 8(c), an inverter with a feedback resistor can play such a role. The pole formed by the input resistance—expressed by (6)—and  $C_D$  should preferably exceed 0.7 $r_b$ , where  $r_b$  is the bit rate. For example, if  $C_D = 50$  fF and  $r_b = 40$  Gb/s, we must have  $R_{in} \approx 114 \Omega$ .

Additionally, the TIA's input-referred noise current must be small enough to yield an acceptable BER for a given received optical power and, hence, a given peak current produced by the photodiode. Neglecting channel length modulation and assuming  $(g_{m1} + g_{m2})R_F \gg 1$ , we can express the noise of the circuit in Figure 14(a) as

$$\overline{I_{n,\text{in}}^2} \approx \frac{4kT\gamma}{(g_{m1}+g_{m2})R_F^2} + \frac{4kT}{R_F}.$$

(10)

Figure 14(b) plots the circuit's transimpedance gain, implying a value of  $51 dB\Omega \equiv 360 \Omega$  and a 3-dB bandwidth of 25 GHz. Presented in Figure 14(c) is the output noise voltage spectrum, whose area from 10 MHz to 100 GHz amounts to  $600 \times 10^{-9} V^2$ . As explained in [5], we divide this value by  $(\pi/2)(360 \Omega)^2(18 \text{ GHz})$  and take the square root, arriving at an inputreferred noise current of  $13 \text{ pA}/\sqrt{\text{Hz}}$ . Figure 14(d) displays the output eye diagram at 40 Gb/s in response to a peak input current of 100  $\mu$ A.

#### References

- F. M. Wanlass, "Low stand-by power complementary field effect circuitry," U.S. Patent 3 356 858, Dec. 5, 1967.

- [2] A. Jain, A. Veggetti, D. Crippa, S. Gerardin, and M. Bagatin, "Radiation tolerant multi-bit flip-flop system with embedded timing pre-error sensing," *IEEE J. Solid-State Circuits*, vol. 57, no. 9, pp. 2878– 2890, Sep. 2022, doi: 10.1109/JSSC.2022. 3149928.

- [3] J. Kim et al., "A 224-Gb/s DAC-based PAM-4 quarter-rate transmitter with 8-tap FFE in 10-nm FinFET," *IEEE J. Solid-State Circuits*, vol. 57, no. 1, pp. 6–20, Jan. 2022, doi: 10.1109/JSSC.2021.3108969.

- [4] J. Im et al., "A 112-Gb/s PAM-4 long-reach wireline transceiver using a 36-way timeinterleaved SAR ADC and inverter-based RX analog front end in 7-nm FinFET," *IEEE J. Solid-State Circuits*, vol. 56, no. 1, pp. 7–18, Jan. 2021, doi: 10.1109/JSSC. 2020.3024261.

- [5] B. Razavi, "The design of a transimpedance amplifier," *IEEE Solid State Circuits Mag.*, vol. 15, no. 1, pp. 7–11, Winter 2023, doi: 10.1109/MSSC.2022.3219682.

SSC

## **EDITOR'S NOTE** (continued from p. 4)

- [A4] S. Oh and M. Je, "Process-scalable and low-power amplifiers," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 55–66, Summer 2024, doi: 10.1109/MSSC.2024. 3416094.

- [A5] A. Sheikholeslami, "Noise and distortion, part I [Circuit intuitions]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 15–18, Summer 2024, doi: 10.1109/MSSC.2024.3419508.

[A6] B. Razavi, "Fifty applications of the CMOS

- [A6] B. Razavi, "Fifty applications of the CMOS inverter—Part 1 [The analog mind]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 7–14, Summer 2024, doi: 10.1109/ MSSC.2024.3419528.

- [A7] C. Mangelsdorf, "Who's afraid of positive feedback? [Shop talk: What you didn't learn in school]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 19–26, Summer 2024, doi: 10.1109/MSSC.2024.3419594.

- [A8] F. Sheikh, "The world of continuous glucose monitors [Circuits from systems perspective]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 27–29, Summer 2024, doi: 10.1109/MSSC.2024.3419595.

- [A9] P. Gray, J. Rabaey, A. Chandrakasan, D. Markovic, and R. Jain, "Remembering Bob Brodersen: Professor, mentor, and pioneer [People]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 68–72,

Summer 2024, doi: 10.1109/MSSC.2024. 3417768.

- [A10] A. Sedra, "Brief history of Sedra/Smith: Microelectronics circuits [Society news]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 75–79, Summer 2024, doi: 10.1109/MSSC.2024.3419488.

- [A11] S. Zargham and D. Dunwell, "The joy of circuits [Society news]," *IEEE Solid-State Circuits Mag.*, vol. 16, no. 3, pp. 73–75, Summer 2024, doi: 10.1109/MSSC.2024. 3417749.