# **Other Effects in PLLs**

Behzad Razavi Electrical Engineering Department University of California, Los Angeles

#### **Example of Up and Down Skew and Width Mismatch**

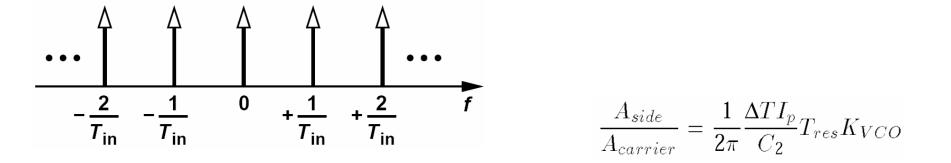

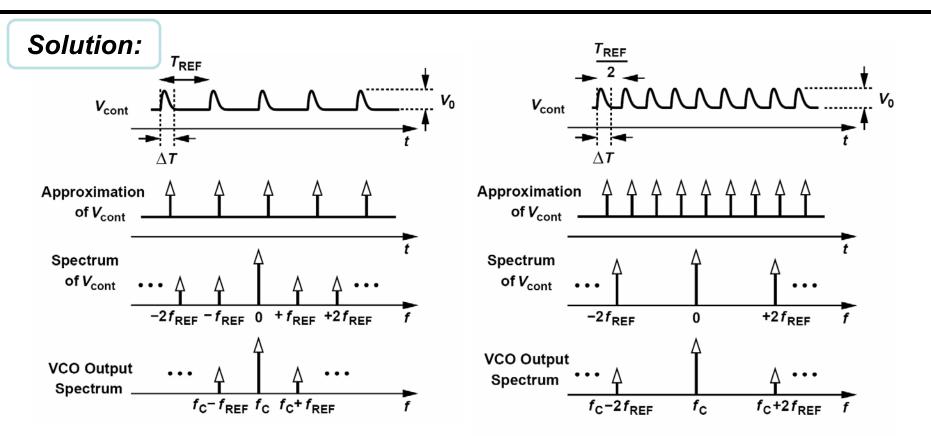

Approximating the pulses on the control line by impulses, determine the magnitude of the resulting sidebands at the output of the VCO.

Sidebands at  $f_c \pm n f_{in}$  are scaled down by a factor of n.

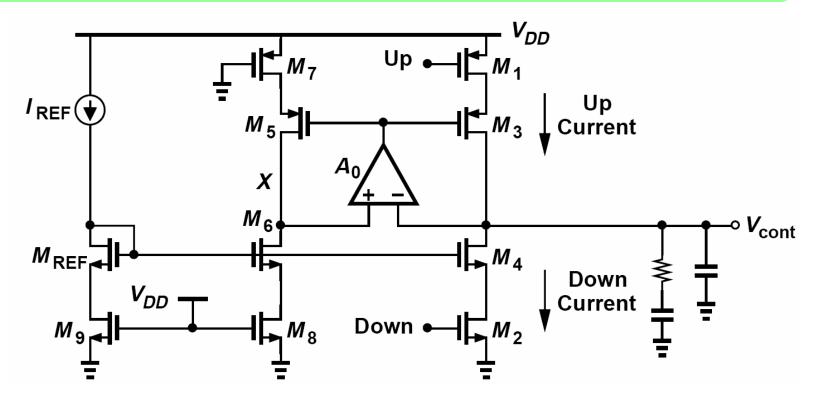

# Circuit Techniques to Deal with Channel Length Modulation: Use of a Servo Loop

A<sub>0</sub> need not provide a fast response

- Performance limited by random mismatches between NMOS current sources and between PMOS current sources.

- Op amp must operate with a nearly rail-to-rail input common-mode range.

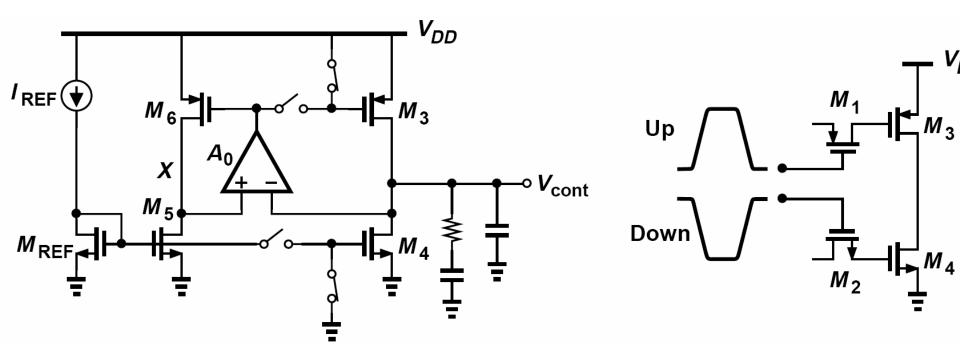

# **Gate Switching**

- Voltage headroom saved

- But exacerbates the problem of Up and Down arrival mismatch.

- Op amp must operate with a wide input voltage range.

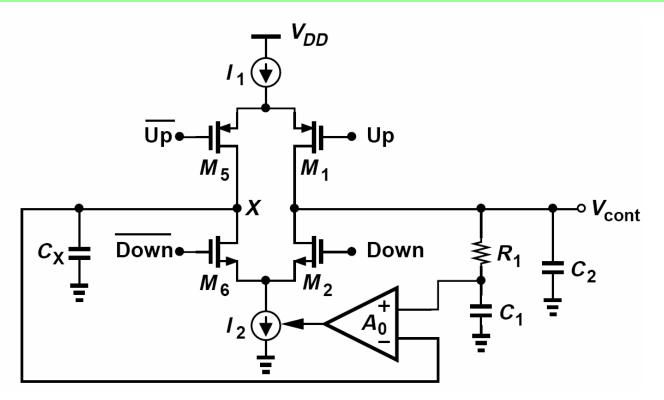

# Another Example that Cancels Both Random and Deterministic Mismatches

> The accuracy of the circuit is ultimately limited by the charge injection and clock feedthrough mismatch between  $M_1$  and  $M_5$  and between  $M_2$  and  $M_6$

### Puzzle

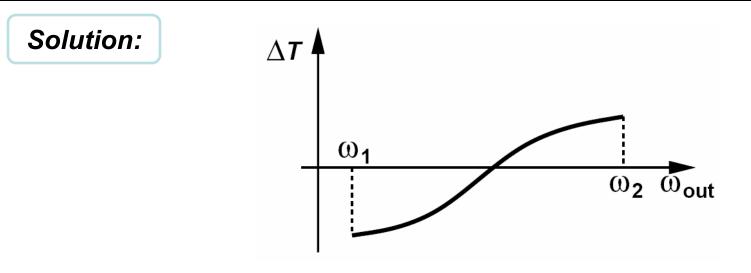

The phase offset of a CPPLL varies with the output frequency. Explain why.

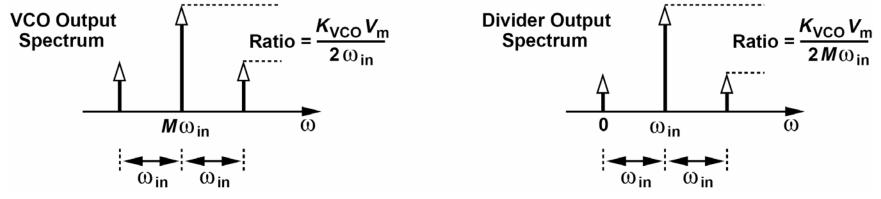

### **Example of Divider Response to FM Sidebands**

The control voltage of a VCO experiences a small sinusoidal ripple of amplitude  $V_m$  at a frequency equal to  $\omega_{in}$ . Plot the output spectra of the VCO and the divider.

$$\begin{split} V_F(t) &= V_0 \cos \left[ \frac{1}{M} (M\omega_{in}t + K_{VCO} \int V_m \sin \omega_{in} t dt) \right] \\ &\approx V_0 \cos \omega_{in} t - \frac{K_{VCO} V_m}{2M\omega_{in}} V_0 \cos(\omega_{in} + \omega_{in}) t + \frac{K_{VCO} V_m}{2M\omega_{in}} V_0 \cos(\omega_{in} - \omega_{in}) t. \end{split}$$

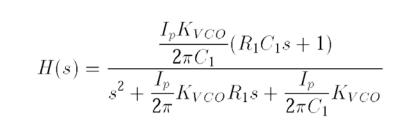

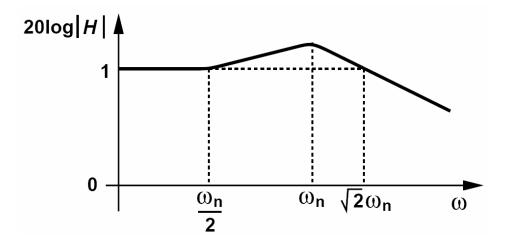

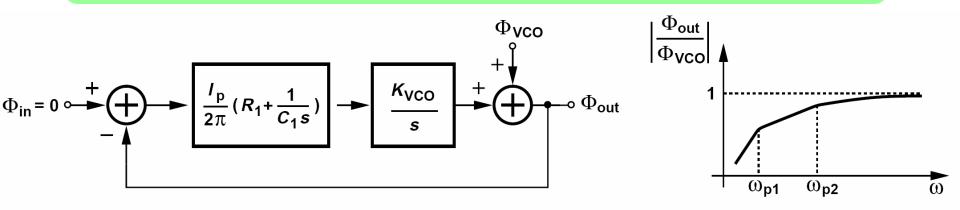

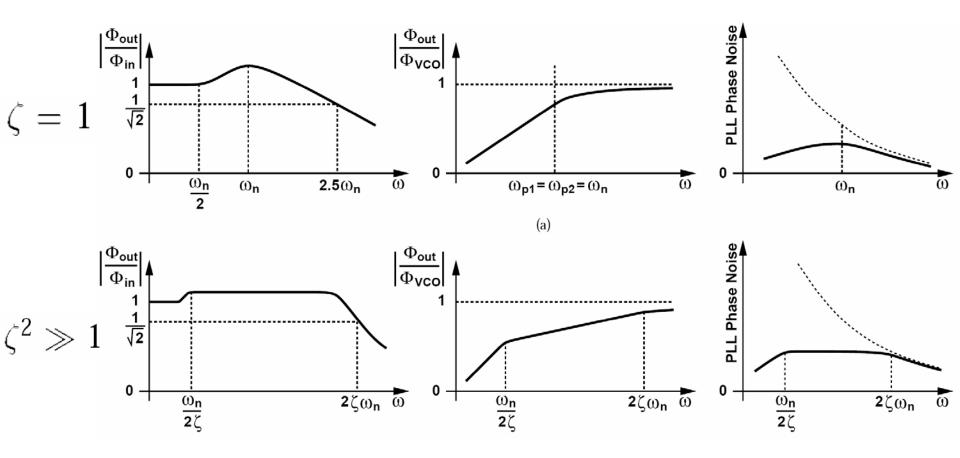

#### **Closed-Loop Freq. Response**

#### Plot the magnitude of the closed-loop transfer function as a function of $\omega$ if $\zeta = 1$

Solution:

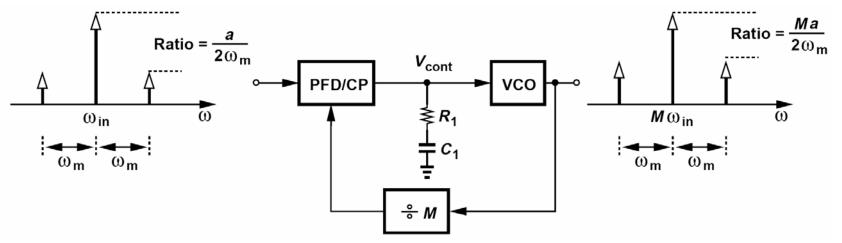

### **Example of Multiplying PLL with FM Input**

The input to a multiplying PLL is a sinusoid with two small "close-in" FM sidebands, i.e., the modulation frequency is relatively low. Determine the output spectrum of the PLL.

$$V_{in}(t) = V_0 \cos(\omega_{in}t + a \int \cos \omega_m t dt)$$

=  $V_0 \cos\left(\omega_{in}t + \frac{a}{\omega_m}\sin \omega_m t\right).$

$$\frac{\phi_{out}}{\phi_{in}}(s\approx 0) = M \quad V_{out}(t) = V_1 \cos\left(M\omega_{in}t + \frac{Ma}{\omega_m}\sin\omega_mt\right)$$

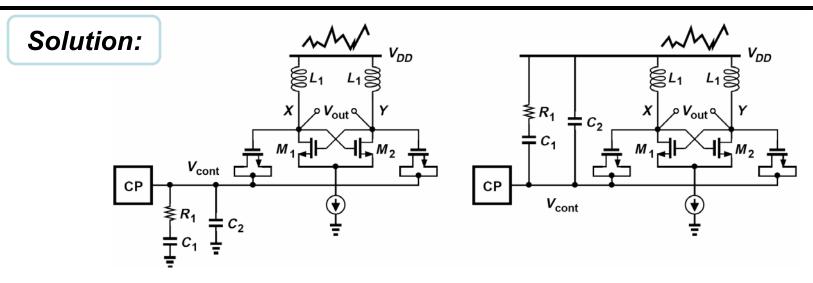

# **Example of Topology to Reject Supply Noise**

Consider the two filter/VCO topologies shown in figure below and explain which one is preferable with respect to supply noise.

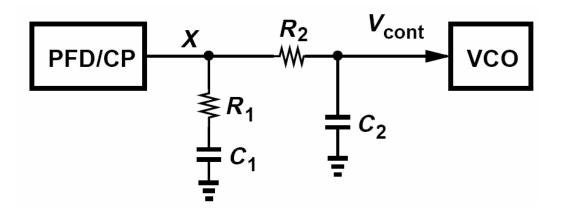

#### **Alternative Second-Order Loop Filter**

$$\mathrm{PM} \approx \tan^{-1}(4\zeta^2) - \tan^{-1}\left(4\zeta^2 \frac{R_2 C_2}{R_1 C_1}\right)$$

- The ripple at node X may be large but it is suppressed as it travels through the low-pass filter consisting of R<sub>2</sub> and C<sub>2</sub>

- >  $(R_2C_2)^{-1}$  must remain 5 to 10 times higher than  $\omega_z$  so as to yield a reasonable phase margin.

### Puzzle

A PLL having a reference frequency of  $f_{REF}$  and a divide ratio of *N* exhibits reference sidebands at the output that are 60 dB below the carrier. If the reference frequency is doubled and the divide ratio is halved (so that the output frequency is unchanged), what happens to the reference sidebands? Assume the CP nonidealities are constant and the time during which the CP is on remains much shorter than  $T_{REF} = 1/f_{REF}$ .

### Phase Noise in PLLs: VCO Phase Noise

$$\frac{\phi_{out}}{\phi_{VCO}} = \frac{s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

### Another Example of VCO Phase Noise(I)

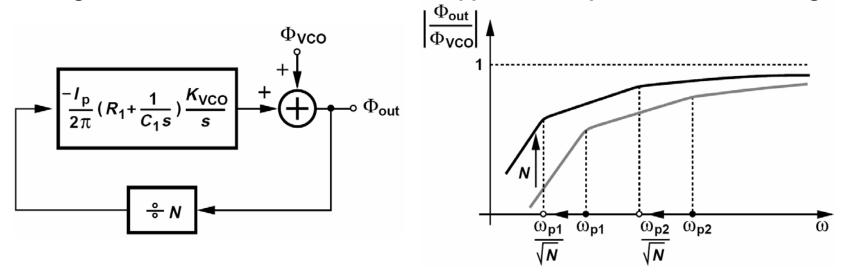

Consider a PLL with a feedback divide ratio of *N*. Compare the phase noise behavior of this case with that of a dividerless loop. Assume the output frequency is unchanged.

Redrawing the loop above as shown below on the left, we recognize that the feedback is now weaker by a factor of *N*. The transfer function still applies, but both  $\zeta$  and  $\omega_n$  are reduced by a factor of  $\sqrt{N}$ .

What happens to the magnitude plot? We make two observations. (1) To maintain the same transient behavior,  $\zeta$  must be constant; e.g., the charge pump current must be scaled up by a factor of *N*. Thus, the poles given by previous equation simply decrease by factor of  $\sqrt{N}$ . (2)For  $s \rightarrow 0$ ,  $\phi_{out}/\phi_{VCO} \approx s^2/\omega_n^2$ , which is a factor of *N* higher than that of the dividerless loop. The magnitude of the transfer function thus appears as depicted below on the right.

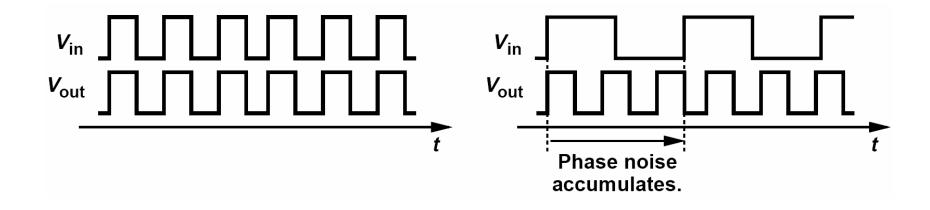

### **Time-Domain Perspective**

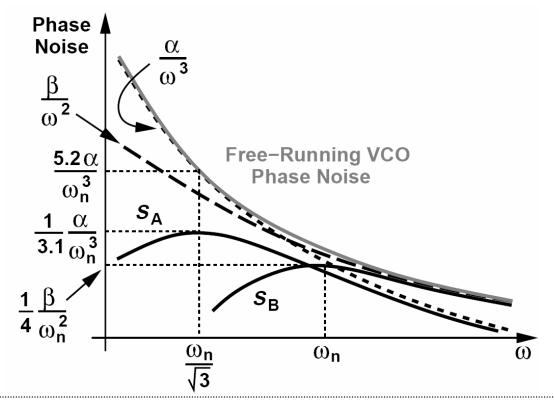

## **VCO Phase Noise: White Noise and Flicker Noise**

$$\overline{\phi}_{out}^2 = \frac{\omega^4}{(\omega^2 - \omega_n^2)^2 + 4\zeta^2 \omega_n^2 \omega^2} \left(\frac{\alpha}{\omega^3} + \frac{\beta}{\omega^2}\right)$$

high offset frequencies

$$\overline{\phi}_{out}^2|_{\text{small }\omega} \approx \frac{\alpha \omega}{(\omega^2 - \omega_n^2)^2 + 4\zeta^2 \omega_n^2 \omega^2}$$

Phase

Noise

$$\frac{1}{3.1} \frac{\alpha}{\omega_n^3} + \frac{\omega}{\sqrt{3}}$$

Free-Running VCO

Phase Noise

$$\frac{1}{\sqrt{3}} \frac{\alpha}{\sqrt{3}} + \frac{\omega}{\omega_n} \frac{\omega}{\omega_n} + \frac{\omega}{\omega_n} \frac{\omega}{\omega_n} + \frac{\omega}{\omega_n} \frac{\omega}{\omega_n} + \frac{\omega}{\omega_n} \frac{\beta}{\omega_n} + \frac{\beta}{\omega_n^2} +$$

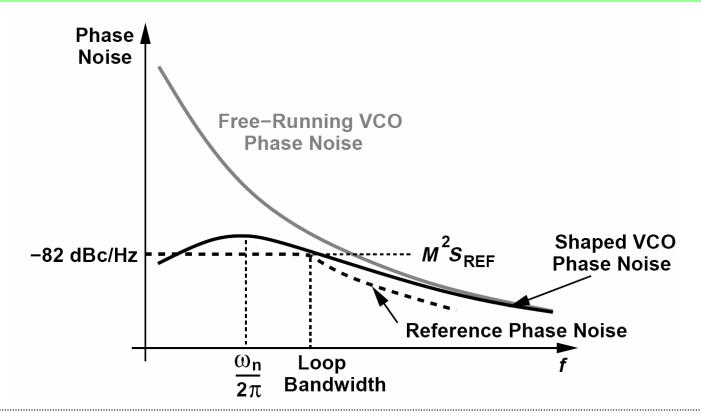

### **Shaped VCO Noise Summary**

$\succ$  The overall PLL output phase noise is equal to the sum of S<sub>A</sub> and S<sub>B</sub>

The actual shape depends on two factors:

(1) the intersection frequency of  $\alpha/\omega^3$  and  $\beta/\omega^2$

(2) the value of  $\omega_n$

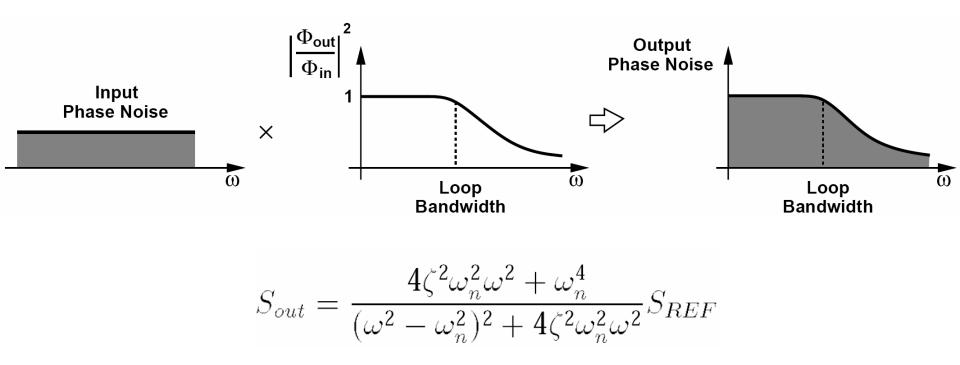

#### **Reference Phase Noise: the Overall Behavior**

Crystal oscillators providing the reference typically display a *flat* phase noise profile beyond an offset of a few kilohertz

### **Reference Phase Noise: Two Observations**

PLLs performing frequency multiplication "amplify" the low-frequency reference phase noise proportionally.

The total phase noise at the output increases with the loop bandwidth

# **Loop Bandwidth**

$$\frac{(2\zeta\omega_n\omega_{-3dB})^2 + \omega_n^4}{(\omega_{-3dB}^2 - \omega_n^2)^2 + (2\zeta\omega_n\omega_{-3dB})^2} = \frac{1}{2} \Longrightarrow$$