# **Layout Considerations**

#### **Basic Issues**

- Analog vs. Digital Supplies

- DC Voltage Drops

- e.g. for 1mm long wire (i.e. 100 sq) and 50m $\Omega$ /sq, this corresponds to: Resistance = 5 $\Omega$

- Bond Wires & Device Capacitances

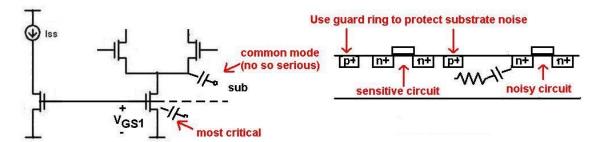

#### -Substrate Coupling

Different arguments for connecting substrate to analog ground and digital ground. Not clear. But the best way is to have a low-inductance connection to substrate.

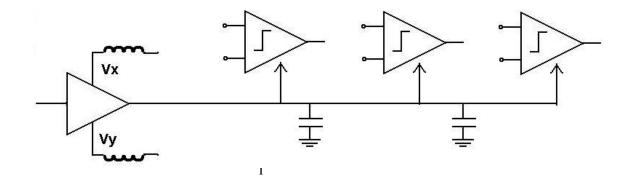

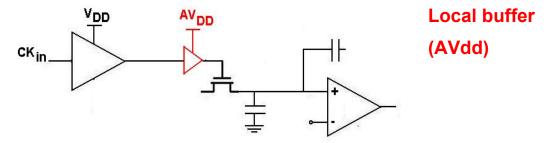

- Clock Noise Coupling

Need a clean buffer.

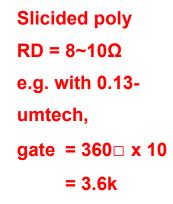

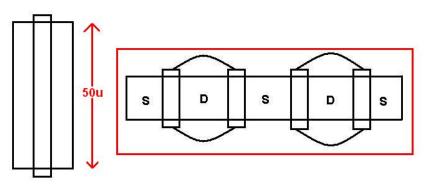

# **Layout of MOS Devices**

- Multi-Finger Structures

EE 215D B.Razavi HO#19

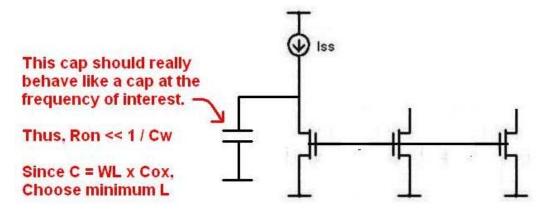

- MOS Devices Used as Capacitors

Do not use if linearity of capacitor is important. Good for bypassing:

But must make sure on-resistance is sufficiently small (Q is high.)

- Measure on-resistance for given gate voltage.

- Divide the value by 12.

Sometimes deliberately choose a low Q to dampen ringing due to bond wire inductance.

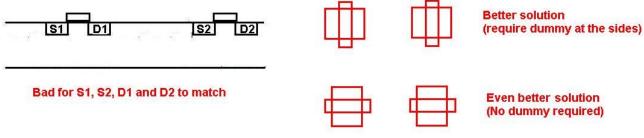

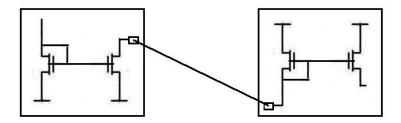

- Matched MOS structures

- Use same orientation

- Account for asymmetries due to nonvertical implants:

EE 215D B.Razavi

- Make the surroundings of transistors the same.

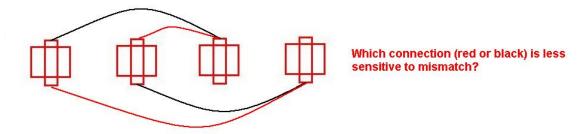

- Cross connect to cancel gradients.

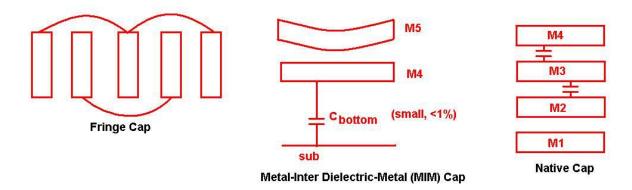

#### **Capacitors**

**Poly-Diffusion**

**Metal-Poly**

"Native Caps"

#### Issues:

Nonlinearity, matching, temp. coefficient, bottom- and topplate parasitics, series resistance, contact placement

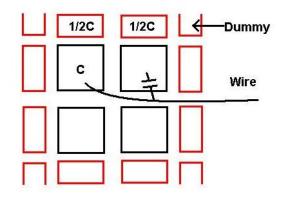

# **Matched Caps**

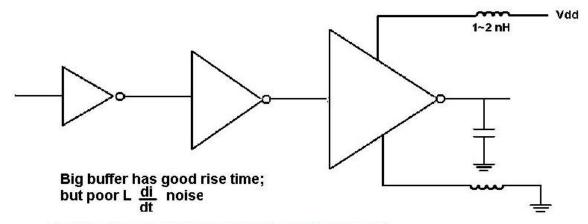

#### **Output Drivers & Clock Buffers**

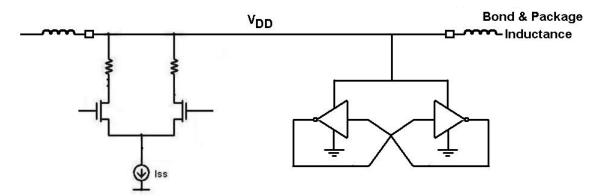

Need to simulate with bond wire inductance to Vdd

- Don't make the driver too large!

- If possible, make the driver differential.

- If possible, reduce the output swing.

In a fully custom-designed system, we can try to route currents rather than voltages.

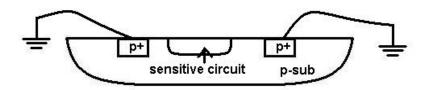

### **Guard Rings**

# Guard ring can be N+, P+ or N-well

Can do the same in n-well. It is also believed that guard rings improve matching as well.

EE 215D B.Razavi

In most modern CMOS technologies, the substrate has a low resisitivity. As a result, the <u>distance</u> between analog and digital blocks has little effect on the amount of coupled noise.

#### **Miscellaneous**

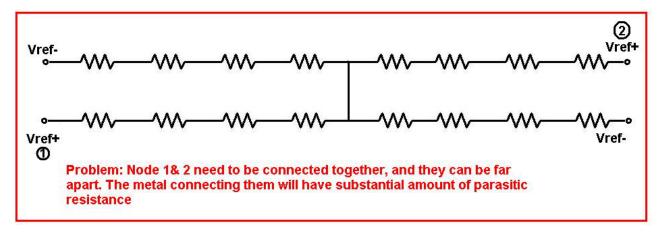

- Resistor Ladder Layout

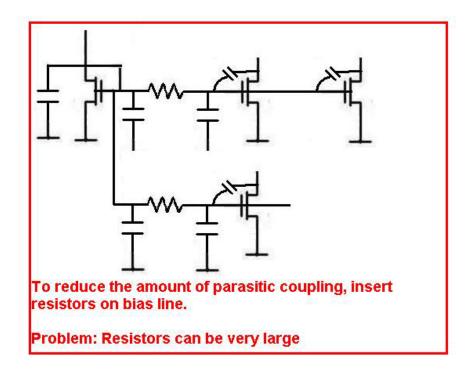

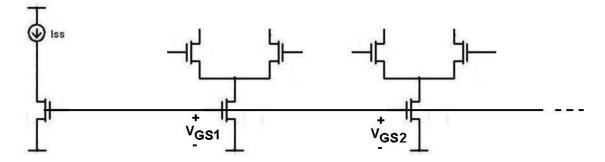

# - Coupling through Bias Line