#### High Speed Channel Coding Architectures for the Uncoordinated OR Channel

#### Herwin Chan, Richard Wesel, Ingrid Verbauwhede UCLA EE Department

Sponsored by Space and Naval Warfare Systems Center – San Diego (N66001-02-1-8938)

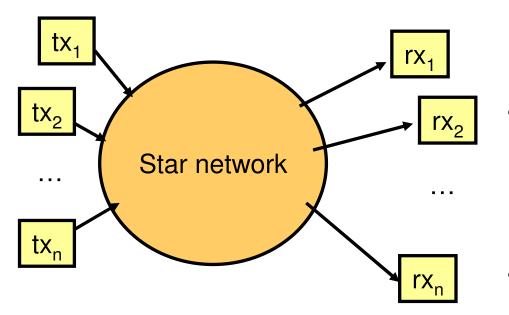

## System Model

Uncoordinated access: transmitters can transmit at any time with any code (chosen from a family) without informing anyone except the desired receiver

- **Optical Channel:**

- 1 : light is transmitted

- 0 : no light is transmitted

UCLA

- Channel Interference: Noncoherent interference is assumed

- 1 : bit will always be correctly received

- 0 : bit can be corrupted by interference

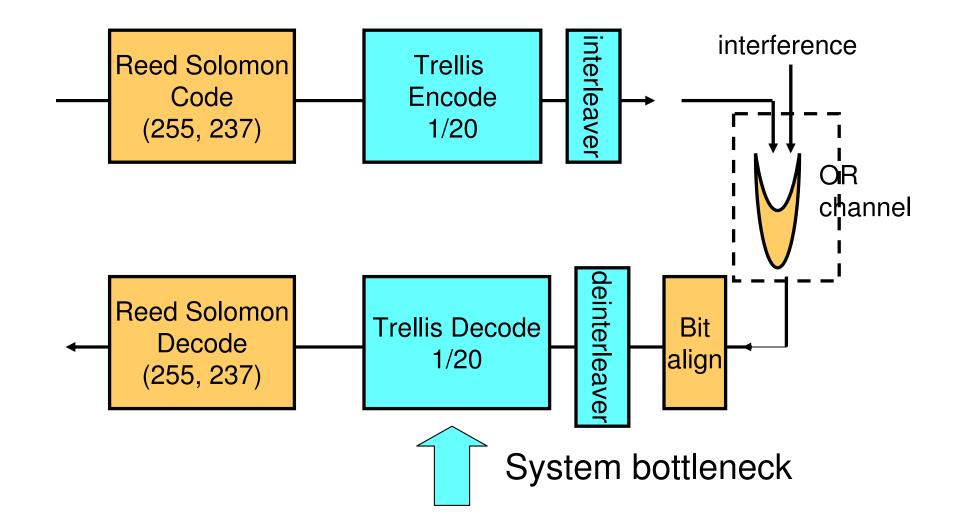

## **Channel Coding Architecture**

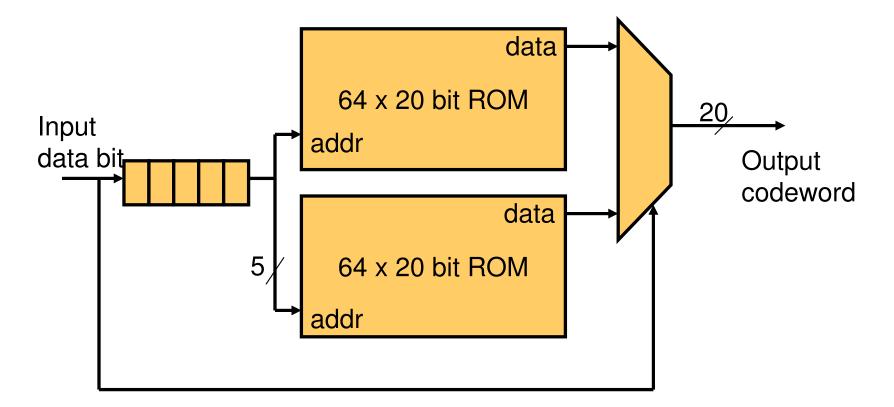

#### **Trellis Encoder**

- Trellis code uses 20 bit words and 64 states

- Fast architecture consists of a shift register to index the codeword memories

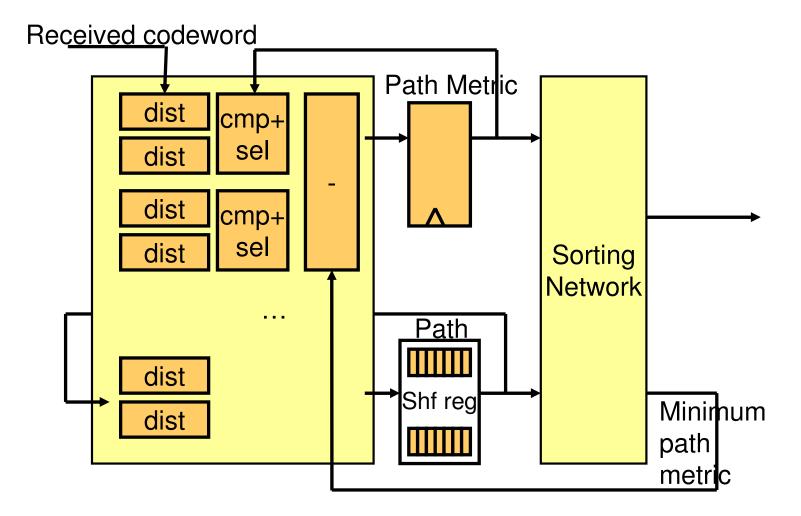

## Viterbi decoder architecture

- All path metrics are calculated and sorted in parallel

- Operations are pipelined to achieve maximum throughput

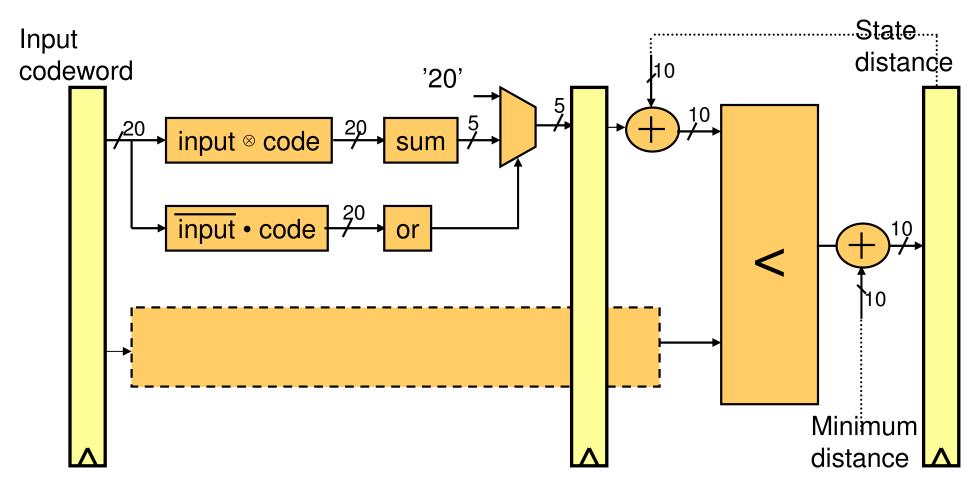

## Calculation of Path Metric

- Special logic is used to calculate path metric of OR channel

- Feedback path of accumulated path metric limits throughput

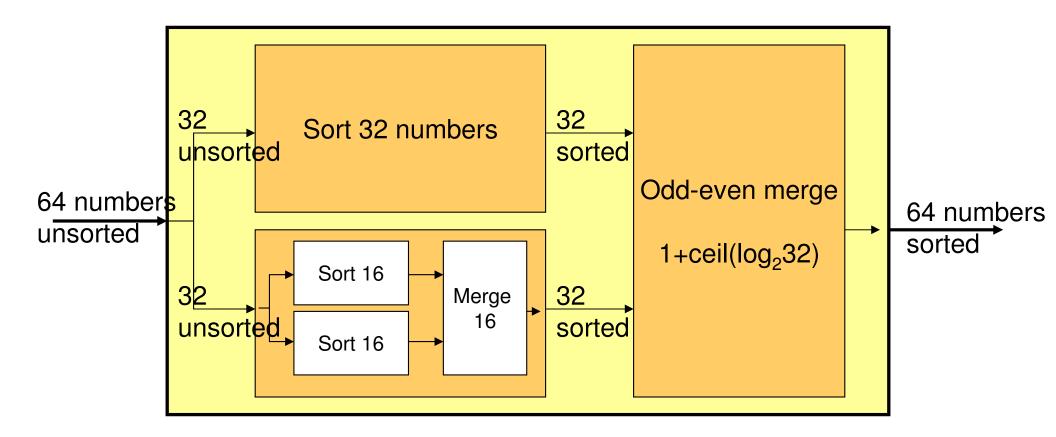

# Sorting Network

- 64 path metrics are sorted using Batcher's algorithm

- Minimum time algorithm minimizes delay in the feedback path

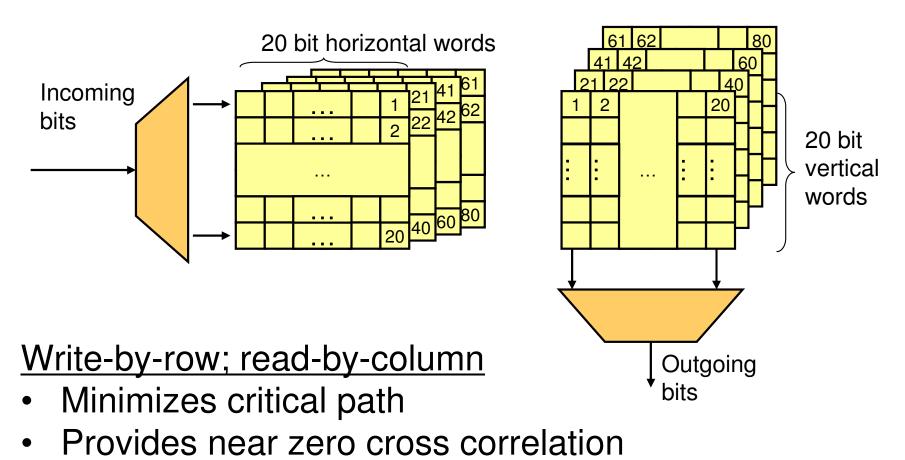

## Interleaver Architecture

• (80!)<sup>2</sup> different permutations possible

## Implementation Results

| VirtexII-Pro FPGA       | Size<br>(slices) | Critical<br>Period<br>(ns) | 0.18um ASIC             | Size<br>(Kgates) | Critical<br>Period<br>(ns) |

|-------------------------|------------------|----------------------------|-------------------------|------------------|----------------------------|

| Transmitter             |                  |                            | Transmitter             |                  |                            |

| Reed Solomon<br>Encoder | 189              | 5.3                        | Reed Solomon<br>Encoder | 3                | 1.6                        |

| NL-TCM Encoder          | 34               | 3.4                        | NL-TCM Encoder          | 9                | 1.3                        |

| Interleaver             | 3389             | 7.7                        | Interleaver             | 39               | 3.7                        |

| Receiver                |                  |                            | Receiver                |                  |                            |

| Reed Solomon<br>Decoder | 3686             | 9.0                        | Reed Solomon<br>Decoder | 29               | 10.3                       |

| NL-TCM decoder          | 10504            | 10.3                       | NL-TCM decoder          | 239              | 1.4                        |

| Interleaver             | 3384             | 7.7                        | Interleaver             | 39               | 3.7                        |

- FPGA able to operate at 2 Gbps channel throughput

- ASIC able to operate at 5.4 Gbps channel throughput

#### Conclusions

- Novel channel codes for the optical OR channel requires design of new architectures

- For optical throughputs, designs must parallelize and pipeline aggressively <u>Viterbi</u>

- Duplication of path metric calculation

- Efficient and pipelined sorting network

- Interleavers

- Write-by-row, Read-by-column strategy

- 2.0 Gbps achieved in FPGA and 5.4 Gbps achieved in ASIC

More info at <u>http://www.ee.ucla.edu/~herwin/ocdma2</u> email at <u>herwin@ee.ucla.edu</u>